Es ist ein technischer Meilenstein: IBM hat den weltweit ersten Chip mit 2-Nanometer-Technologie entwickelt.

Chips gehören zu unserem Alltag und sind in fast jedem Gerät zu finden, das wir nutzen – von Mobiltelefonen, intelligenten Haushaltsgeräten und Autos bis hin zu Servern in Rechenzentren. Die Nachfrage nach immer schnelleren, energieeffizienteren Geräten, die mit Chips betrieben werden, wächst in Zeiten von Künstlicher Intelligenz, Machine Learning, dem Internet der Dinge und Cloud-Computing ins Unermessliche.

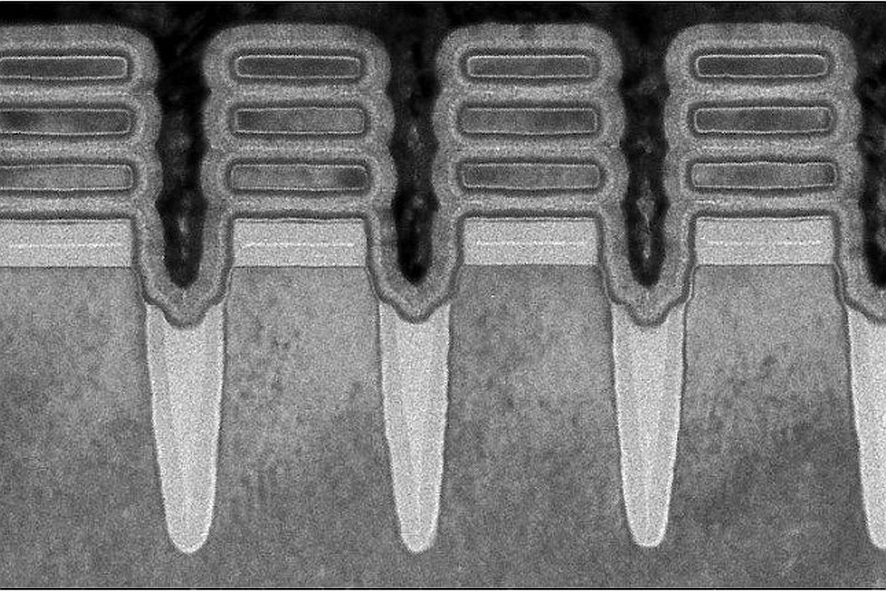

Auf dem Chip sind dank einer raffinierten 3D-Technik auf der Fläche einer Briefmarke rund 50 Milliarden Transistoren untergebracht. Zur Veranschaulichung: Ein Nanometer ist ein Milliardstel Meter. Mit der 2-nm-Technologie können 50 Milliarden Transistoren auf einem Chip von der Größe eines Fingernagels untergebracht werden. Auf einem 300-mm-Chipwafer befinden sich damit fast zehnmal mehr 2-nm-Transistoren als es Bäume gibt. Mit der weltweit kleinsten Architektur hat dieser der neue 2-nm-Chip eine um 45% höhere Leistung und einen um 75% niedrigeren Energieverbrauch als die heute verfügbaren 7-nm-Chips.

Die Erwartungen sind hoch, denn dieses Chipdesign wird die Grundlage für zukünftige Systeme von IBM als auch von anderen Herstellern sein.

Diese Technologie könnte u.a.

- den CO2-Fußabdruck von Rechenzentren verringern, deren Energieverbrauch immer weiter steigt.

- Mobiltelefone drastisch beschleunigen – bis hin zu einer schnelleren 5G- oder 6G-Verbindung.

- die Akkulaufzeit von Mobiltelefonen vervierfachen.

- die Ladezeiten und Funktionen von Laptops drastisch beschleunigen.

- eine schnelle Objekterkennung und Reaktionszeit in autonomen Fahrzeugen ermöglichen.

IBM Research hat die 2-nm-Technologie in seinem Forschungszentrum in Albany im US-Bundesstaat New York entwickelt, einem der modernsten Halbleiterforschungseinrichtungen der Welt. Hier hat IBM ein öffentlich-privates Innovationsnetzwerk aufgebaut, zu dem neben dem Staat New York auch Konzerne wie Samsung Electronics und seit kurzem auch Intel gehören. Alle haben Interesse daran, die Grenzen der sog „Logikskalierung“ zu erweitern und die Forschung und Entwicklung in den Bereichen Halbleiter-Design, Prototyping, Packaging und Fertigung voranzutreiben.

Mehr Transistoren auf einem Chip bedeuten auch, dass Prozessordesigner mehr Möglichkeiten haben, Innovationen auf Kernebene einzubringen, um die Fähigkeiten für führende Workloads wie KI und Cloud-Computing zu verbessern, sowie neue Wege für hardwaregestützte Sicherheit und Verschlüsselung.

09.05.2021